ซอฟต์แวร์สำหรับช่วยออกแบบวงจรรวม หรือ Electronic Design Automation เป็นเครื่องมือที่สำคัญอย่างยิ่งในการช่วยเหลือให้นักออกแบบสามารถทำงานได้รวดเร็วขึ้น สามารถจัดการกับวงจรที่มีขนาดใหญ่และซับซ้อนได้ แต่ปัญหาราคาเครื่องมือสำหรับออกแบบในเชิงพาณิชย์นั้นยังมีราคาอยู่ในระดับที่สูงมาก จนทำให้บริษัทขนาดกลางและเล็ก (SME) ไม่สามารถจัดหาหรือเป็นเจ้าของเองได้ จึงเป็นอุปสรรคต่องานวิจัยและพัฒนาองค์ความรู้และการพัฒนาบุคลากรในภาคการศึกษาและการวิจัยและพัฒนาผลิตภัณฑ์ในภาคเอกชนไทยส่งผลให้ขีดความสามารถในการแข่งขันของเอกชนไทยลดต่ำลง

ศูนย์พัฒนาธุรกิจออกแบบวงจรรวม (TIDI) มองเห็นความสำคัญของปัญหานี้ จึงได้ดำเนินการโครงการในการเป็นผู้จัดหาคอมพิวเตอร์สมรรถนะสูงและซอฟต์แวร์สำหรับช่วยในการออกแบบวงจรรวมทั้งหมดไว้ในส่วนกลาง และให้ผู้ใช้หรือนักออกแบบหรือนักพัฒนาวงจรรวมสามารถเข้ามาใช้งานได้ในราคาที่เหมาะสม เพื่อให้เอกชนมีค่าลงทุนเริ่มต้นที่ไม่สูงมากสำหรับการเริ่มต้นการวิจัยและพัฒนาผลิตภัณฑ์ นับว่าเป็นการใช้ประโยชน์สูงสุดจากเครื่องมือเหล่านี้ให้เกิดผลต่อการพัฒนาเศรษฐกิจของประเทศ

|

ประเภทของการใช้งาน |

ซอฟต์แวร์ |

คุณลักษณะ |

|

FPGA Development |

ModelSim SE |

โปรแกรมจำลองการทำงานของวงจรบน PC จากบริษัท Mentor Graphics |

|

FPGA Advantage |

เครื่องมือออกแบบ FPGA คุณภาพสูงบน PC จากบริษัท Mentor Graphics |

|

Leonardo Spectrum |

เครื่องมือออกแบบ FPGA คุณภาพสูงบน PC จากบริษัท Mentor Graphics |

|

Xilinx ISE 4.1i |

เครื่องมือออกแบบ FPGA คุณภาพสูงบน PC และ Sun จากบริษัท Xilinx |

|

Quartus 2/Max Plus II |

เครื่องมือออกแบบ FPGA คุณภาพสูงบน PC จากบริษัท Altera |

|

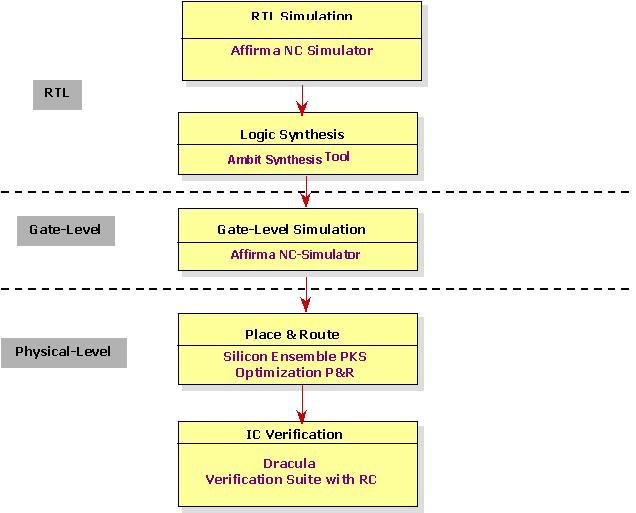

Functional Verification |

Cadence(R) NC-Sim mixed language simulator REL LDV 3.3 |

โปรแกรมจำลองการทำงานของวงจรที่ใช้กับภาษาพรรณนาฮาร์ดแวร์ได้ทั้ง VHDL และ Verilog และใช้กับวงจรได้ทั้ง analog และ digital โปรแกรมนี้ใช้ขั้นตอนวิธี Native-Compiled ซึ่งทำ simulation ได้รวดเร็วมาก มี debugger ที่ดีช่วยให้ค้นพบจุดบกพร่องในโปรแกรมได้ง่าย เหมาะสมสำหรับการออกแบบ SoC |

|

Synthesis |

Ambit(R) BuildGates(R) synthesis SPR |

โปรแกรมสังเคราะห์วงจรจากภาษาพรรณนาฮาร์ดแวร์ระดับ RTL ที่สังเคราะห์วงจรดิจิทัลขนาดใหญ่กว่าหลายล้านเกตได้อย่างรวดเร็วและถูกต้อง รองรับการออกแบบให้ทดสอบได้ (DFT) มี Datapath Synthesis Option ที่ช่วยทำให้ datapath logic เหมาะที่สุด มี Low Power Synthesis Option ช่วยให้วงจรกินไฟน้อย |

|

Place and Route |

Silicon Ensemble(TM) PKS optimization place-and-route DSM SE5.3. |

โปรแกรมจัดวางและเชื่อมโยง สำหรับการออกแบบวงจรแบบ semi-custom ที่ใช้ standard cell เป็นพื้นฐาน สามารถทำงานร่วมกับ Ambit BuildGates ได้เป็นอย่างดี ทำให้ได้กระบวนการสังเคราะห์ จัดวางและเชื่อมโยง (SP&R) ที่เป็นเอกภาพ |

|

|

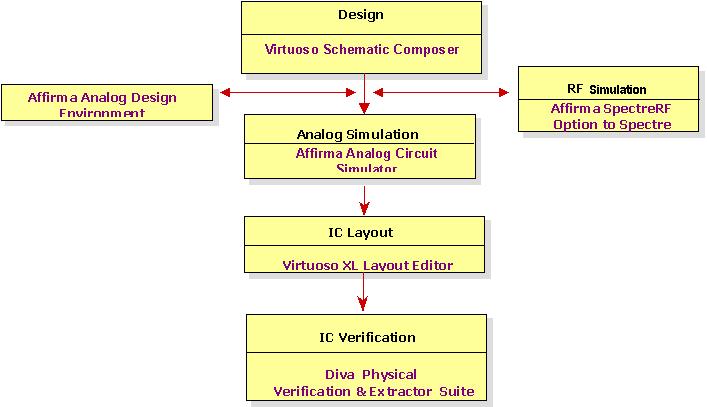

Analog and

Mixed-Signal

Design |

Virtuoso® schematic composer IC 4.46 |

โปรแกรมสร้างและแก้ไขแผนภาพเค้าร่าง (schematic) ของวงจรแบบกราฟิก รองรับการออกแบบวงจร mixed-signal ได้อย่างดี รองรับการออกแบบเป็นทีม |

|

Cadence ® Analog Design Environment IC 4.46 |

โปรแกรมจัดสภาพแวดล้อมสำหรับออกแบบวงจร analog และ RF แบบ full-custom จากส่วนหน้าไปส่วนหลัง Analog Design Environment รวมเอาโปรแกรมเครื่องมือช่วยออกแบบที่จำเป็นทุกตัวมาไว้ในสภาพแวดล้อมเดียวกัน รวมทั้ง post-processing tool สำหรับการวิเคราะห์ผล และ scripting language สำหรับ non-graphical environment |

|

Spectre(R) circuit simulator IC 4.46 |

โปรแกรมจำลองการทำงานของวงจร analog ซึ่งให้ความถูกต้อง (accuracy) ความลู่เข้า (convergence) และ สมรรถนะที่ดีกว่า ด้วยการประมวลผลและแสดงผลล่วงหน้า รองรับการใช้ภาษา Verilog-A สำหรับการจำลองเชิงพฤติกรรม |

|

Spectre(R) RF simulation option IC 4.46 |

ตัวเลือกเสริมโปรแกรม Spectre สำหรับจำลองการทำงานของวงจร RF สามารถทำ full-chip simulation ได้อย่างรวดเร็ว เหมาะสำหรับวงจรเพื่อการสื่อสารแบบไร้สายที่นำสมัย สามารถทำนายผลทั้งใน frequency domain และ time domain ได้อย่างรวดเร็ว รองรับการออกแบบแบบ top-down รองรับภาษา Verilog-A และรองรับการวิเคราะห์แบบ Monte Carlo |

|

Cadence(R) analog HSPICE interface option IC |

ส่วนต่อประสานกับ Analog Design Environment ที่รองรับการใช้ภาษา HSPICE เพื่อการจำลองการทำงานของวงจร |

|

Custom

IC Layout |

Virtuoso(R) XL layout editor IC |

โปรแกรมสร้างและแก้ไขลวดลายผังวงจร (layout) ที่ทรงประสิทธิภาพ มีฟังก์ชันสำหรับการวาดและแก้ไข polygon ครบถ้วนสมบูรณ์ ทำให้สามารถวางผังวงจรได้อย่างรวดเร็วและถูกต้อง ทำงานร่วมกับโปรแกรมอื่นๆของ Cadence ได้ดี รองรับการใช้เซลล์ที่ปรับขนาดตามตัวแปรเสริม (parameterized cell) |

|

Physical Verification |

Diva(R) physical verification and extractor suite IC |

โปรแกรมตรวจสอบความถูกต้องระดับกายภาพ (DRC, ERC, LVS) สำหรับผังวงจร analog และผังวงจรแบบ full-custom ที่ติดต่อโต้ตอบกับผู้ใช้แบบ interactive โปรแกรมนี้ทำงานร่วมกับ Virtuoso และ Analog Design Environment ได้เป็นอย่างดี |

|

Dracula(R) physical verification and extractor suite IC 4.46 |

โปรแกรมตรวจสอบความถูกต้องระดับกายภาพ (DRC, ERC, LVS) สำหรับผังวงจรขนาดใหญ่หรือใหญ่มาก (VLSI) เช่นวงจรดิจิทัล รองรับระบบ distributed processing ที่ทำให้การตรวจสอบใช้เวลาน้อยลง มี GUI ที่ใช้งานง่าย และให้ output ที่เป็นมาตรฐานสำหรับการจำลองการทำงานหลัง layout และการวิเคราะห์บูรณภาพของสัญญาณ |